IBM et 3M veulent construire des « building » de processeurs

IBM et 3M ont mis au point une « colle » qui permet d'empiler les microprocesseurs afin d'en démultiplier la puissance à surface de connexion égale.

Un pas de géant se profile pour développer des systèmes surpuissants en ressources microprocesseurs. Lorsqu'on parle de densité d'intégration dans le domaine de la micro-électronique, on pense à une réduction de la longueur de grille des transistors MOS accompagnée d'une augmentation de la densité d'interconnexion de ces mêmes transistors. IBM et 3M vont peut-être chambouler cette manière de penser grâce à un nouveau type de colle.

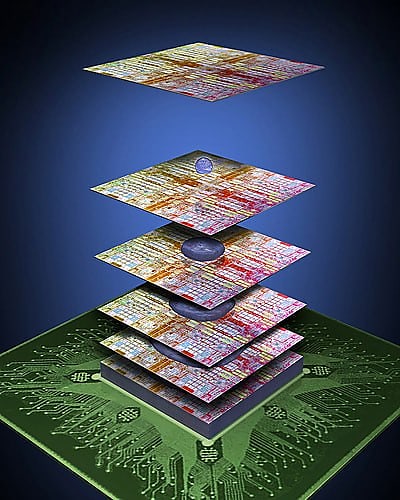

Les deux acteurs se sont inspirés de l'architecture des buildings des grandes villes nés de la nécessité d'augmenter la densité de bureaux pour une surface donnée et limitée. IBM et 3M collaborent sur un procédé de collage du silicium qui participe du même principe. Il s'agirait d'une nouvelle classe de matériaux qui permettrait d'empiler les puces : par exemple une tour de 100 puces n'occuperait donc que la surface d'une seule de ces puces (mais un volume global inévitablement revu à la hausse), rapporte Gizmodo.fr.On imagine le bond phénoménal que cela engendrerait en termes de densité d'intégration.

Des choses sont déjà faites en « 3D », notamment du côté d'Intel et sa technologie « tri-gate ». Mais il s'agit plus de transistors 3D qui fonctionnent de façon similaire aux transistors 2D. En revanche, le MOS possédant une telle grille 3D serait ainsi 37 % plus performant que son équivalent planar.

Ce procédé de collage des puces permettrait selon IBM « d'obtenir des CPU jusqu'à 1000 fois plus puissants qu'actuellement ». Les problèmes techniques relèvent de l'évacuation de la chaleur, du bonding (les connexions qui vont de la puce au boîtier) ainsi que des inter-connexions entre les différentes puces.

Si IBM et 3M réussissent à produire de telles puces à des coûts raisonnables, c'est peut-être une quatrième loi de Moore qu'il faudra formuler (la troisième confirmant que « la puissance double tous les dix-huit mois à investissements constants »).

Sur le même thème

Voir tous les articles Business