UMC rejoint l'alliance d'IBM pour le 10 nm FinFET

Le fondeur taïwanais UMC vient d'annoncer une collaboration avec IBM portant sur le développement de la technologie CMOS avancée 10 nm à transistors FinFET.

C'est par un communiqué publié sur son site qu'United Microelectronics Corp (UMC) annonce rejoindre le groupe IBM Technology Development Alliances dans le cadre du développement de la technologie CMOS 10 nm à transistors tridimensionnels FinFET.

Le 10 nm rejoint le 14 nm sur la feuille de route d'UMC

En 2012 déjà, UMC avait collaboré au développement du process 20 nm. Ce dernier a ensuite été requalifié en technologie 14 nm, car basée alors sur des étapes de fabrication avec cette finesse tandis que la seconde partie du processus de fabrication, le back end of line (BEOL), restait en 20 nm.

UMC annonce ainsi que le FinFET 14 nm continuera à être amélioré en interne afin d'obtenir un process « faible puissance » pour l'électronique mobile. D'autre part, le fondeur taïwanais précise qu'il dépêchera une équipe d'ingénieurs à Albany dans l'État de New York afin de participer aux travaux de développement de la technologie 10 nm à transistors FinFET.

« Fondée il y a une décennie, IBM alliance permet aux partenaires de tirer parti de notre expertise combinée, de la recherche collaborative et le développement de technologies innovantes pour répondre aux besoins les plus exigeants pour les applications à semi-conducteurs avancés« , a déclaré Gary Patton, vice-président de la R & D semi-conducteurs au sein d'IBM, dans un communiqué publié par UMC.

IBM se félicite également de la collaboration de UMC au 10 nm : « UMC constitue un partenaire important pour l'alliance. »

Poursuivre la loi de Moore

Tant UMC qu'IBM sont restés laconiques sur la technologie 10 nm. Toutefois, il pourrait s'agir de SOI (Silicon on Insulator), un choix qui serait alors proche de celui de STMicroelectronics qui poursuit la fabrication de circuits intégrés avec des technologies avancées FD-SOI (Fully Depleted Silicon on Insulator).

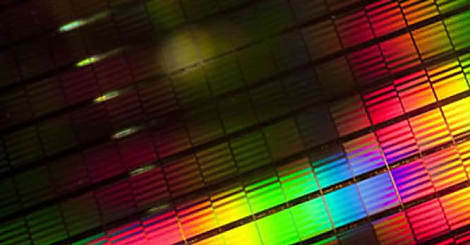

Le mois dernier, c'est TSMC qui annonçait que les premiers wafers 16 nm (à transistors FinFET également) sortiraient de fab avant la fin 2013. GlobalFoundries et Intel capitaliseront, eux, sur le 14 nm. Intel a d'ailleurs un die shrink en 14 nm des processeurs Haswell sur sa feuille de route. Pour précision, les process 16 nm et 14 nm de TSMC et de GloFo reposent également sur des étapes BEOL en 20 nm.

La finesse de gravure apparaît bien comme un enjeu majeur pour les différents fondeurs qui repoussent sans cesse les limites de la lithographie grâce à différents procédés. Il en va du rapport performance par watt qui découle directement de cette finesse et de l'augmentation du nombre de puces par wafer.

Il n'en reste pas moins que les investissements sont au moins inversement proportionnels aux finesses de gravure. Ne subsisteront donc que les plus puissants capables d'investir des budgets faramineux en R&D et de créer des lignes d'assemblage dotées d'équipements toujours plus onéreux. UMC entend bien être de ceux-là.

Sur le même thème

Voir tous les articles Workspace