ARM dévoile l'interface AMBA 5 CHI pour CPU Cortex-A50

Sur les bases du protocole AMBA 4 ACE, ARM a annoncé au DAC 2013 la spécification de l'AMBA 5 CHI destiné à servir d'interface à des processeurs ARM 64 bits.

Le protocole AMBA 5 CHI (Coherent Hub Interface) dont la spécification a été dévoilée au salon DAC 2013 par ARM, doit permettre à des processeurs ARM 64 bits Cortex-A50 de fonctionner de concert dans des agencements à haute performance.

AMBA 5 CHI pour une cohérence des systèmes multi SoC

Si la technologie big.LITTLE assure un fonctionnement cohérent de coeurs hétérogènes dans le cadre de processeurs mobiles, le protocole AMBA 5 CHI a été développé pour des systèmes de plus en plus vastes basés sur des topologies complexes d'interconnexion.

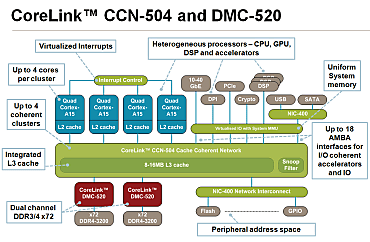

Il a été élaboré pour fonctionner avec les processeurs ARM 64 bits Cortex-A57 et Cortex-A53, et le DMC (Dynamic Memory Controller) Corelink DMC-520. Il est également utilisé par le CoreLink CCN-504 Cache Coherent Network, qui autorise des flux de données de 1 Terabit/s.

Dans le cadre de serveurs, il vise ainsi à assurer les débits requis en environnement professionnel. À cet effet, l'interface régie par ce protocole assure une performance optimale du système en supportant les caches distribués de niveau 3, des débits très élevés via les E/S et la fonctionnalité de qualité de service (QoS).

Lire aussi : Vers des puces ARM 64 bits à 32 cours ?

Un protocole développé avec les partenaires d'ARM

AMBA 5 CHI a été développé par les partenaires semi-conducteurs d'ARM, les fournisseurs tiers de propriétés intellectuelles (IP) et l'industrie EDA (Electronic Design Automation) dont Mentor Graphics.

«Afin de s'assurer que nos partenaires de silicium puissent rapidement déployer des IP et des SoC mettant en oeuvre le protocole AMBA 5 CHI, ARM a travaillé en étroite collaboration avec de nombreux partenaires à travers l'écosystème de conception SoC», explique Noel Hurley, vice-président, Marketing et Stratégie, Division processeur, ARM.

«Grâce à l'engagement précoce, nous avons permis à nos partenaires EDA de développer un large éventail d'outils de Verification IP, de débogage et d'analyse de performance pour accélérer l'implémentation des SoC basés sur AMBA 5 CHI.»

L'architecture AMBA 5 CHI introduit également un modèle en couches afin de séparer les protocoles de communication et de transport, ce qui permet le compromis optimal entre les performances, la puissance et la surface.

La spécification du protocole AMBA CHI 5 et les vérificateurs de protocole associés (assertions SystemVerilog) sont disponibles, sans frais, sous licence aux entreprises intégrant ou développant une IP qui implémente le protocole AMBA 5 CHI.

Sur le même thème

Voir tous les articles Workspace